This single character can provide shift-left in your coverage closure cycle - SystemVerilog dist, PySlint

In SystemVerilog based testbenches, functional coverage models and constraint models are like the yin and yang.

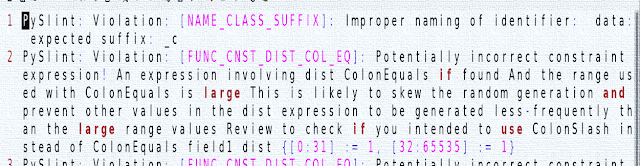

In a good testbench, coverage model should specify what-to-observe using coverpoints/bins/crosses. An accompanying transaction model would capture transaction attributes along with constraints on variables and their relationships. This is specifically applicable to the input/stimuli-based coverage models. As part of coverage closure cycle, verification engineers run the random generator multiple times and measure the progress using coverage metrics. At times this cycle takes far too long and one of the possible causes could be wrong coding/models to begin with. It can be too-wide a state-space modeled using coverage constructs or too tight a constraint model (over constrained). Using static analysis one can identify a set of issues in coverage model and/or constraint model. Let's take a case study of a wrong constraint model as shown below:

class data; rand bit [15:0] field1; constraint c_f1 { field1 dist {[0:31] := 1, [32:65535] := 1};} endclass

(This example is picked from https://stackoverflow.com/questions/70438473/systemverilog-dist-constraint). Syntactically the above code looks just fine. However, as the user found (by running simulations many times):

I'm trying to get an equal weight between two ranges [0:31] and [32:65535]. However, I'm seeing most values > 32. What have I misunderstood here?

Plotting this as distribution, roughly one could visualize as below - while the user wanted a uniform distribution of values, some skewed behavior was observed.

Jumping guns, let's see what PySlint can tell us about this code:PySlint: Violation: [FUNC_CNST_DIST_COL_EQ]: Potentially incorrect constraint expression! An expression involving dist ColonEquals is found, and the range used with ColonEquals is large. This is likely to skew the random generation and prevent other values in the dist expression to be generated less-frequently than the large range values Review to check if you intended to use ColonSlash instead of ColonEquals

field1 dist {[0:31] := 1, [32:65535] := 1}

So, PySlint flags a potential issue - a mix-up of ColonEquals vs. ColonSlash operator in SystemVerilog distribution constraint. Below is an extract from IEEE 1800 SystemVerilog LRM:

So, in a nutshell, when the range is large (say more than 10), using ColonEquals in dist can lead to skewed results in randomization and most likely user's intention would have been to have more spread about distribution as below:

But as the user in that StackOverFlow post/thread realized, such subtle coding issues can lead to loss of productivity. Imagine the same being used in a larger IP such as PCIe, USB etc. - this can have significant impact on coverage closure cycle due to a subtle mix-up of ColonEQ vs. ColonSlash. So, when in doubt - do not beat your random generator to death, instead get innovative and look for static code analysis such as PySlint!

Comments

Post a Comment