Using MathLib in Artificial Intelligence systems - computing sqrt in Matlab vs. SystemVerilog

Consider an AI (Artificial Intelligence) engine trying to decipher key information from a series of images in real-time. Fourier transform is a powerful tool used to analyze and manipulate images in the frequency domain. The Fourier transform of an image result in a complex-valued representation, consisting of real and imaginary components. To visualize the frequency content of the image or perform further analysis, it is common to calculate the magnitude of this complex representation. This is done by computing the square-root (sqrt) of the sum of the squares of its real and imaginary components. By applying the sqrt function to the complex image representation, we can obtain the magnitude image.

At system level, Matlab is commonly used to model such algorithms. Matlab's sqrt works with both positive and negative numbers, which is different from a typical IEEE 754 standard. While SystemVerilog has a built-in system function $sqrt() - it works only with scalars and does not handle negative numbers - it returns NaN (Not-a-Number) - in accordance with IEEE 754. However, while verifying/modeling such intelligent algorithms, one needs to match the behavior of Matlab as reference model. Below is a snippet from Matlab's documentation on this key deviation:

Now, using $sqrt in SystemVerilog would not match your reference models from Matlab. We at AsFigo have been helping customers verify such designs and have built the comprehensive library named MathLib that includes Matlab compatible functions such as sqrt.

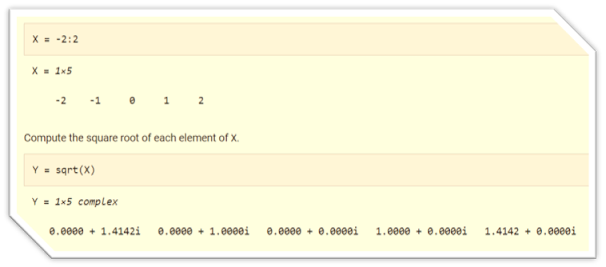

Below is a reference example from Matlab:

And with MathLib, below is a sample result for same values:

So, next time when you need to verify complex blocks involving mathematical models especially the ones developed with Matlab reference models, call us to get MathLib to help verify your designs faster!

Comments

Post a Comment