Porting a complete UVC to Verilator + UVM - an anecdote!

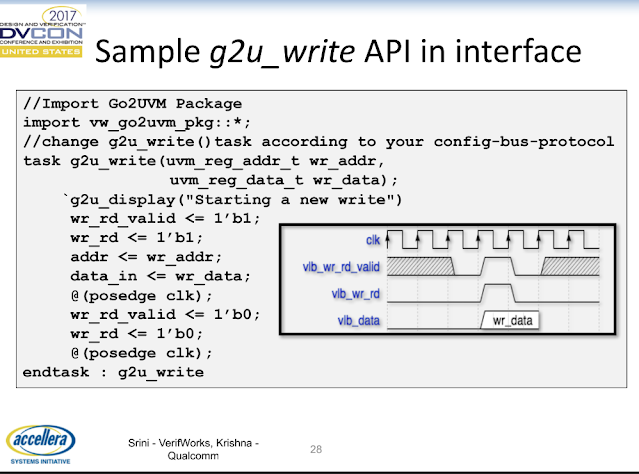

So, here we are on Day-1 of UVM + Verilator becoming available to the public, start of democratizing chip design verification. In case you just woke-up/started on this topic, read the release of UVM + Verilator with some intricate details on the challenge on the way by Antmicro via: https://antmicro.com/blog/2023/10/running-simple-uvm-testbenches-in-verilator/ Awesome work by the folks at Antmicro and fantastic support by the ecosystem specifically Western Digital, kudos! At AsFigo , we are committed to fueling open-source driven chip design and verification. So we took this opportunity to port a commercial-grade UVC (Universal Verification Component or a Verification IP) and ported it to compile and run on Verilator. Below are our reflections from this experiment. Get in touch with us to discuss how AsFigo can help your VIPs and testbenches to be ported to opensource EDA. Case study: VLBus - a simple peripheral bus intended for write/read to configuration...